# FM32278/276/274/272

5V Integrated Processor Companion with Memory

# Features

#### **High Integration Device Replaces Multiple Parts**

- Serial Nonvolatile Memory

- Low Voltage Reset

- Watchdog Timer

- Early Power-Fail Warning/NMI

- Two 16-bit Event Counters

- Serial Number with Write-lock for Security

#### **Processor Companion**

- Active-low Reset Output for V<sub>DD</sub> and Watchdog

- Programmable V<sub>DD</sub> Reset Trip Point

- Manual Reset Filtered and Debounced

- Programmable Watchdog Timer

- Dual Battery-backed Event Counter Tracks System Intrusions or other Events

- Comparator for Early Power-Fail Interrupt

- 64-bit Programmable Serial Number with Lock

# Description

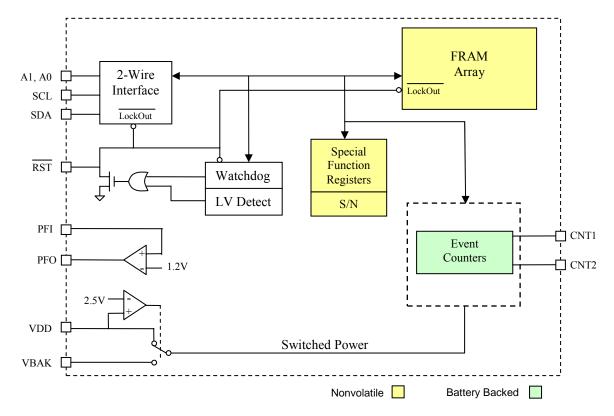

The FM3227x is a family of integrated devices that includes the most commonly needed functions for processor-based systems. Major features include nonvolatile memory available in various sizes, low-VDD reset, watchdog timer, nonvolatile event counter, lockable 64-bit serial number area, and general purpose comparator that can be used for an early power-fail (NMI) interrupt or other purpose. The family operates from 4.0 to 5.5V.

The FM3227x family is software and pinout compatible with the FM3127x family which also includes a real-time clock. The common features allow a system design that easily can be assembled with or without timekeeping by simply selecting the FM3127x or FM3227x, respectively.

Each FM3227x provides nonvolatile RAM available in sizes including 4Kb, 16Kb, 64Kb, and 256Kb versions. Fast write speed and unlimited endurance allow the memory to serve as extra RAM or conventional nonvolatile storage. This memory is truly nonvolatile rather than battery backed.

#### Ferroelectric Nonvolatile RAM

- 4Kb, 16Kb, 64Kb, and 256Kb versions

- Unlimited Read/Write Endurance

- 10 year Data Retention

- NoDelay<sup>TM</sup> Writes

#### **Fast Two-wire Serial Interface**

- Up to 1 MHz Maximum Bus Frequency

- Supports Legacy Timing for 100 kHz & 400 kHz

- Device Select Pins for up to 4 Memory Devices

- Companion Controlled via 2-wire Interface

#### **Easy to Use Configurations**

- Operates from 4.0 to 5.5V

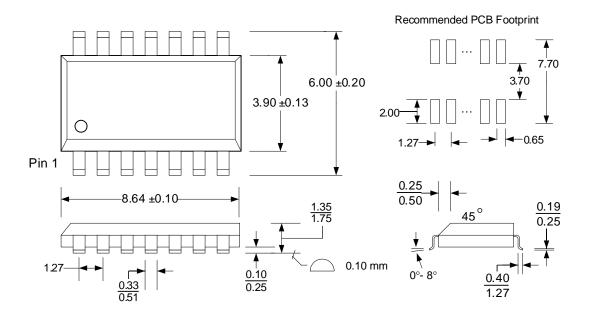

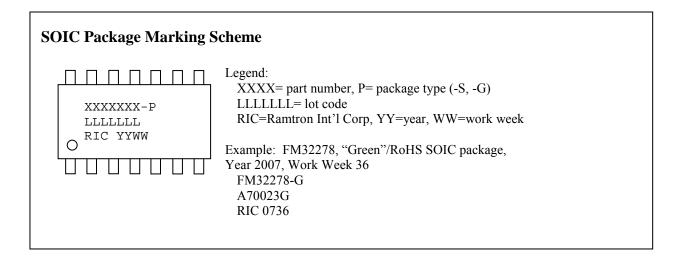

- 14-pin "Green"/RoHS SOIC package (-G)

- Pin Compatible with FM3127x Series

- Low Operating Current

- -40°C to +85°C Operation

The processor companion includes commonly needed CPU support functions. Supervisory functions include a reset output signal controlled by either a low VDD condition or a watchdog timeout. /RST goes active when VDD drops below a programmable threshold and remains active for 100 ms after VDD rises above the trip point. A programmable watchdog timer runs from 100 ms to 3 seconds. The watchdog timer is optional, but if enabled it will assert the reset signal for 100 ms if not restarted by the host before the timeout. A flag-bit indicates the source of the reset.

A general-purpose comparator compares an external input pin to the onboard 1.2V reference. This is useful for generating a power-fail interrupt (NMI) but can be used for any purpose. The family also includes a programmable 64-bit serial number that can be locked making it unalterable.

Additionally the FM3227x offers a dual event counter that tracks the number of rising or falling edges detected on dedicated input pins. The counter can optionally be battery backed and even battery operated by attaching a backup power source to the VBAK pin. If VBAK is connected to a battery or capacitor, then events will be counted even in the absence of  $V_{\rm DD}$ .

This is a product in pre-production phase of development. Device characterization is complete and Ramtron does not expect to change the specifications. Ramtron will issue a Product Change Notice if any specification changes are made.

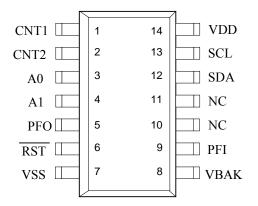

# **Pin Configuration**

| Pin Name   | Function                |

|------------|-------------------------|

| CNT1, CNT2 | Event Counter Inputs    |

| A0, A1     | Device Select inputs    |

| PFO        | Early Power-Fail Output |

| /RST       | Reset Input/Output      |

| PFI        | Early Power-fail Input  |

| SDA        | Serial Data             |

| SCL        | Serial Clock            |

| VBAK       | Battery-Backup Supply   |

| VDD        | Supply Voltage          |

| VSS        | Ground                  |

| Ordering Information |             |                   |                 |                      |  |  |

|----------------------|-------------|-------------------|-----------------|----------------------|--|--|

| Base Configuration   | Memory Size | Operating Voltage | Reset Threshold | Ordering Part Number |  |  |

| FM32278              | 256Kb       | 4.0-5.5V          | 3.9, 4.4V       | FM32278-G            |  |  |

| FM32276              | 64Kb        | 4.0-5.5V          | 3.9, 4.4V       | FM32276-G            |  |  |

| FM32274              | 16Kb        | 4.0-5.5V          | 3.9, 4.4V       | FM32274-G            |  |  |

| FM32272              | 4Kb         | 4.0-5.5V          | 3.9, 4.4V       | FM32272-G            |  |  |

Other memory configurations may be available. Please contact the factory for more information.

#### **Pin Descriptions**

| Pin Name   | Туре   | Pin Description                                                                                                                                                                                                                                                                                                                              |

|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0, A1     | Input  | Device select inputs are used to address multiple memories on a serial bus. To select<br>the device the address value on the two pins must match the corresponding bits<br>contained in the device address. The device select pins are pulled down internally.                                                                               |

| CNT1, CNT2 | Input  | Event Counter Inputs: These battery-backed inputs increment counters when an edge is detected on the corresponding CNT pin. The polarity is programmable. These pins should not be left floating. Tie to ground if pins are not used.                                                                                                        |

| PFO        | Output | Power Fail Output: This is the early power-fail output.                                                                                                                                                                                                                                                                                      |

| /RST       | I/O    | Active low reset output with weak pull-up. Also input for manual reset.                                                                                                                                                                                                                                                                      |

| SDA        | I/O    | Serial Data & Address: This is a bi-directional line for the two-wire interface. It is open-drain and is intended to be wire-OR'd with other devices on the two-wire bus. The input buffer incorporates a Schmitt trigger for noise immunity and the output driver includes slope control for falling edges. A pull-up resistor is required. |

| SCL        | Input  | Serial Clock: The serial clock line for the two-wire interface. Data is clocked out of the part on the falling edge, and in on the rising edge. The SCL input also incorporates a Schmitt trigger input for noise immunity.                                                                                                                  |

| PFI        | Input  | Early Power-fail Input: Typically connected to an unregulated power supply to detect<br>an early power failure. This pin should not be left floating.                                                                                                                                                                                        |

| VBAK       | Supply | Backup supply voltage: A 3V battery or a large value capacitor. If no backup supply is used, this pin should be tied to ground and the VBC bit should be cleared.                                                                                                                                                                            |

| VDD        | Supply | Supply Voltage                                                                                                                                                                                                                                                                                                                               |

| VSS        | Supply | Ground                                                                                                                                                                                                                                                                                                                                       |

# Overview

The FM3227x family combines a serial nonvolatile RAM with a processor companion. The companion is a highly integrated peripheral including a processor supervisor, a comparator used for early power-fail warning, nonvolatile event counters, and a 64-bit serial number. The FM3227x integrates these complementary but distinct functions that share a common interface in a single package. Although monolithic, the product is organized as two logical devices, the F-RAM memory and the companion. From the system perspective they appear to be two separate devices with unique IDs on the serial bus.

The FM3227x provides the same functions as the FM3127x with the exception of the real-time clock. This makes it easy to develop a common design that can either include timekeeping by using the FM3127x or exclude it by using the FM3227x. All other features are identical. The register address map is even preserved so that software can be identical.

The memory is organized as a stand-alone 2-wire nonvolatile memory with a standard device ID value. The companion functions are accessed under their own 2-wire device ID. This allows the companion functions to be read while maintaining the most recently used memory address. The companion functions are controlled by 16 special function registers. The event counter circuits and related registers are maintained by the power source on the VBAK pin, allowing them to operate from battery or backup capacitor power when  $V_{DD}$  drops below a set threshold. Each functional block is described below.

# **Memory Operation**

The FM3227x is a family of products available in different memory sizes including 4Kb, 16Kb, 64Kb, and 256Kb. The family is software compatible, all versions use consistent two-byte addressing for the memory device. This makes the lowest density device different from its stand-alone memory counterparts but makes them compatible within the entire family.

Memory is organized in bytes, for example the 4Kb memory is 512 x 8 and the 256Kb memory is 32,768 x 8. The memory is based on F-RAM technology. Therefore it can be treated as RAM and is read or written at the speed of the two-wire bus with no delays for write operations. It also offers effectively unlimited write endurance unlike other nonvolatile memory technologies. The 2-wire interface protocol is described further on page 13.

The memory array can be write-protected by software. Two bits in the processor companion area

(WP0, WP1 in register 0Bh) control the protection setting as shown in the following table. Based on the setting, the protected addresses cannot be written and the 2-wire interface will not acknowledge any data to protected addresses. The special function registers containing these bits are described in detail below.

| Write protect addresses | WP1 | WP0 |

|-------------------------|-----|-----|

| None                    | 0   | 0   |

| Bottom 1/4              | 0   | 1   |

| Bottom 1/2              | 1   | 0   |

| Full array              | 1   | 1   |

# **Processor Companion**

In addition to nonvolatile RAM, the FM3227x family incorporates a highly integrated processor companion. It includes a low voltage reset, a programmable watchdog timer, battery-backed event counters, a comparator for early power-fail detection or other purposes, and a 64-bit serial number.

#### **Processor Supervisor**

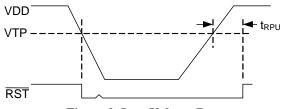

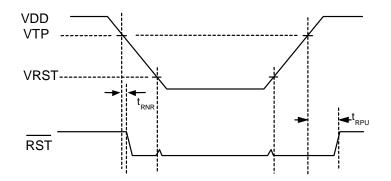

Supervisors provide a host processor two basic functions: detection of power supply fault conditions and a watchdog timer to escape a software lockup condition. All FM3227x devices have a reset pin (/RST) to drive the processor reset input during power faults (and power-up) and software lockups. It is an open drain output with a weak internal pull-up to V<sub>DD</sub>. This allows other reset sources to be wire-OR'd to the /RST pin. When V<sub>DD</sub> is above the programmed trip point, /RST output is pulled weakly to  $V_{DD}$ . If  $V_{DD}$  drops below the reset trip point voltage level (V<sub>TP</sub>) the /RST pin will be driven low. It will remain low until  $V_{DD}$  falls too low for circuit operation which is the  $V_{RST}$  level. When  $V_{DD}$  rises again above V<sub>TP</sub>, /RST will continue to drive low for at least 100 ms  $(t_{RPU})$  to ensure a robust system reset at a reliable  $V_{DD}$  level. After  $t_{RPU}$  has been met, the /RST pin will return to the weak high state. While /RST is asserted, serial bus activity is locked out even if a transaction occurred as V<sub>DD</sub> dropped below V<sub>TP</sub>. A memory operation started while  $V_{DD}$  is above  $V_{TP}$ will be completed internally.

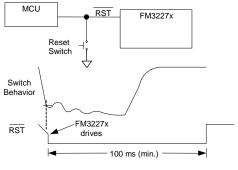

Figure 2 below illustrates the reset operation in response to the  $V_{DD}$  voltage.

Figure 2. Low Voltage Reset

The bit VTP controls the trip point of the low voltage detect circuit. It is located in register 0Bh, bit 0. Note that the bit 1 location is a "don't care".

| <u>V<sub>TP</sub></u> | VTP |

|-----------------------|-----|

| 3.9V                  | 0   |

| 4.4V                  | 1   |

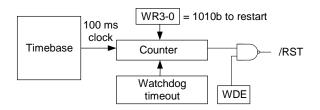

The watchdog timer can also be used to assert the reset signal (/RST). The watchdog is a free running programmable timer. The period can be software programmed from 100 ms to 3 seconds in 100 ms increments via a 5-bit nonvolatile register. All programmed settings are minimum values and vary with temperature according to the operating specifications. The watchdog has two additional controls associated with its operation, a watchdog enable bit (WDE) and timer restart bits (WR). Both the enable bit must be set and the watchdog must timeout in order to drive /RST active. If a reset event occurs, the timer will automatically restart on the rising edge of the reset pulse. If WDE=0, the watchdog timer runs but a watchdog fault will not cause /RST to be asserted low. The WTR flag will be set, indicating a watchdog fault. This setting is useful during software development and the developer does not want /RST to drive. Note that setting the maximum timeout setting (11111b) disables the counter to save power. The second control is a nibble that restarts the timer preventing a reset. The timer should be restarted after changing the timeout value.

The watchdog timeout value is located in register 0Ah, bits 4-0, and the watchdog enable is bit 7. The watchdog is restarted by writing the pattern 1010b to the lower nibble of register 09h. Writing this pattern will also cause the timer to load new timeout values. Writing other patterns to this address will not affect its operation. Note the watchdog timer is freerunning. Prior to enabling it, users should restart the timer as described above. This assures that the full timeout period will be set immediately after enabling. The watchdog is disabled when  $V_{DD}$  is below  $V_{TP}$ . The following table summarizes the watchdog bits.

| Watchdog timeout | WDT4-0 | 0Ah, bits 4-0 |

|------------------|--------|---------------|

| Watchdog enable  | WDE    | 0Ah, bit 7    |

| Watchdog restart | WR3-0  | 09h, bits 3-0 |

Figure 3. Watchdog Timer

#### **Manual Reset**

The /RST pin is bi-directional and allows the FM3227x to filter and de-bounce a manual reset switch. The /RST input detects an external low condition and responds by driving the /RST signal low for 100 ms.

Figure 4. Manual Reset

Note that an internal weak pull-up on /RST eliminates the need for additional external components.

#### **Reset Flags**

In case of a reset condition, a flag will be set to indicate the source of the reset. A low  $V_{DD}$  reset or manual reset is indicated by the POR flag, register 09h bit 6. A watchdog reset is indicated by the WTR flag, register 09h bit 7. Note that the flags are internally set in response to reset sources, but they must be cleared by the user. When the register is read, it is possible that both flags are set if both have occurred since the user last cleared them.

#### **Early Power Fail Comparator**

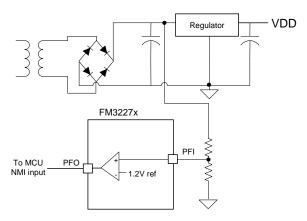

An early power fail warning can be provided to the processor well before  $V_{DD}$  drops out of spec. The comparator is used to create a power fail interrupt (NMI). This can be accomplished by connecting the PFI pin to the unregulated power supply via a resistor divider. An application circuit is shown below.

Figure 5. Comparator as Early Power-Fail Warning

#### RAMTRON

The voltage on the PFI input pin is compared to an onboard 1.2V reference. When the PFI input voltage drops below this threshold, the comparator will drive the PFO pin to a low state. The comparator has 100 mV (max) of hysteresis to reduce noise sensitivity, only for a rising PFI signal. For a falling PFI edge, there is no hysteresis.

The comparator is a general purpose device and its application is not limited to the NMI function.

Note: The maximum voltage on the comparator input PFI is limited to 3.75V under normal operating conditions.

#### **Event Counter**

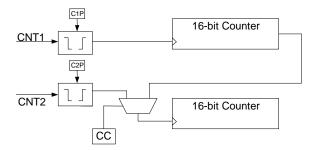

The FM3227x offers the user two battery-backed event counters. Input pins CNT1 and CNT2 are programmable edge detectors. Each clocks a 16-bit counter. When an edge occurs, the counters will increment their respective registers. Counter 1 is located in registers 0Dh and 0Eh, Counter 2 is located in registers 0Fh and 10h. These register values can be read anytime VDD is above VTP, and they will be incremented as long as a valid VBAK power source is provided. To read, set the RC bit register 0Ch bit 3 to 1. This takes a snapshot of all four counter bytes allowing a stable value even if a count occurs during the read. The registers can be written by software allowing the counters to be cleared or initialized by the system. Counts are blocked during a write operation. The two counters can be cascaded to create a single 32-bit counter by setting the CC control bit (register 0Ch). When cascaded, the CNT1 input will cause the counter to increment. CNT2 is not used in this mode.

**Figure 6. Event Counter**

The control bits for event counting are located in register 0Ch. Counter 1 Polarity is bit C1P, bit 0; Counter 2 Polarity is C2P, bit 1; the Cascade Control is CC, bit 2; and the Read Counter bit is RC bit 3.

The polarity bits must be set prior to setting the counter value(s). If a polarity bit is changed, the counter may inadvertently increment. If the counter pins are not being used, tie them to ground.

#### Serial Number

A memory location to write a 64-bit serial number is provided. It is a writeable nonvolatile memory block that can be locked by the user once the serial number is set. The 8 bytes of data and the lock bit are all accessed via the device ID for the processor companion. Therefore the serial number area is separate and distinct from the memory array. The serial number registers can be written an unlimited number of times, so these locations are general purpose memory. *However once the lock bit is set the values cannot be altered and the lock cannot be removed*. Once locked the serial number registers can still be read by the system.

The serial number is located in registers 11h to 18h. The lock bit is SNL, register 0Bh bit 7. Setting the SNL bit to a 1 disables writes to the serial number registers, and *the SNL bit cannot be cleared*.

#### **Backup Power**

The event counter and battery-backed registers may be powered with a backup power source. When the primary system power fails, the voltage on the  $V_{DD}$  pin will drop. When  $V_{DD}$  is less than 2.5V, the event counters and battery-backed registers will switch to the backup power supply on  $V_{BAK}$ .

A battery may be inserted into a system board without any concern for excessive current draw on the FM3227x's  $V_{BAK}$  pin.

# **Trickle Charger**

To facilitate capacitor backup, the  $V_{BAK}$  pin can optionally provide a trickle charge current. When the VBC bit, register 0Bh bit 2, is set to '1', the  $V_{BAK}$  pin will source approximately 80  $\mu$ A until  $V_{BAK}$  reaches 3.75V. In 5V systems, this charges the capacitor to  $V_{DD}$  without an external diode and resistor charger and also prevents the user from exceeding the  $V_{BAK}$ maximum voltage specification. There is a Fast Charge mode which is enabled by the FC bit (register 0Bh, bit 5). In this mode the trickle charger current is set to approximately 1 mA, allowing a large backup capacitor to charge more quickly.

In the case where no backup source is used, the  $V_{BAK}$  pin should be tied to  $V_{SS}$ .  $V_{BAK}$  should not be tied to 5V since the  $V_{BAK}$  (max) specification will be exceeded. Be sure to turn off the trickle charger (VBC=0), otherwise charger current will be shunted to ground from  $V_{DD}$ .

<sup>b</sup> Note: systems using lithium batteries should clear the VBC bit to 0 to prevent battery charging. The  $V_{BAK}$  circuitry includes an internal 1 K $\Omega$  series resistor as a safety element.

#### **Register Map**

The processor companion functions are accessed via 16 special function registers mapped to a separate 2-wire device ID. The interface protocol is described below. The registers contain timekeeping data, control bits, or information flags. A description of each register follows the summary table below.

#### **Register Map Summary Table**

Battery-backed =  $\square$ Nonvolatile =

| Address | D7  | D6  | D5    | D4                                       | D3     | D2   | D1   | D0   | Function            | Range |  |

|---------|-----|-----|-------|------------------------------------------|--------|------|------|------|---------------------|-------|--|

| 18h     |     |     |       | Serial Number 7                          | FFh    |      |      |      |                     |       |  |

| 17h     |     |     | Seria | al Number E                              | Byte 6 |      |      |      | Serial Number 6     | FFh   |  |

| 16h     |     |     | Seria | al Number E                              | Byte 5 |      |      |      | Serial Number 5     | FFh   |  |

| 15h     |     |     | Seria | al Number E                              | Byte 4 |      |      |      | Serial Number 4     | FFh   |  |

| 14h     |     |     | Seria | al Number E                              | Byte 3 |      |      |      | Serial Number 3     | FFh   |  |

| 13h     |     |     | Seria | al Number E                              | Byte 2 |      |      |      | Serial Number 2     | FFh   |  |

| 12h     |     |     | Seria | al Number E                              | Byte 1 |      |      |      | Serial Number 1     | FFh   |  |

| 11h     |     |     | Seria | al Number E                              | Byte 0 |      |      |      | Serial Number 0     | FFh   |  |

| 10h     |     |     | С     | ounter 2 MS                              | SB     |      |      |      | Event Counter 2 MSB | FFh   |  |

| 0Fh     |     |     | С     | ounter 2 LS                              | BB     |      |      |      | Event Counter 2 LSB | FFh   |  |

| 0Eh     |     |     | С     | ounter 1 MS                              | SB     |      |      |      | Event Counter 1 MSB | FFh   |  |

| 0Dh     |     |     | С     | ounter 1 LS                              | SB     |      |      |      | Event Counter 1 LSB | FFh   |  |

| 0Ch     |     |     |       |                                          | RC     | CC   | C2P  | C1P  | Event Count Control |       |  |

| 0Bh     | SNL | -   | FC    | WP1                                      | WP0    | VBC  | -    | VTP  | Companion Control   |       |  |

| 0Ah     | WDE | -   | -     | WDT4                                     | WDT3   | WDT2 | WDT1 | WDT0 | Watchdog Control    |       |  |

| 09h     | WTR | POR | LB    | - WR3 WR2 WR1 WR0 Watchdog Restart/Flags |        |      |      |      | S                   |       |  |

| 00-08h  |     |     |       | RESERVED                                 |        |      |      |      |                     |       |  |

\*Note that the usable address range starts at address 09h to preserve software compatibility with the FM3127x device family, which includes a real-time clock in registers 00-08h.

Note: When the device is first powered up and programmed, all registers must be written because the batterybacked register values cannot be guaranteed. The table below shows the default values of the non-volatile registers. All other register values should be treated as unknown.

| Default R | egister Values |

|-----------|----------------|

| Address   | Hex Value      |

| 18h       | 0x00           |

| 17h       | 0x00           |

| 16h       | 0x00           |

| 15h       | 0x00           |

| 14h       | 0x00           |

| 13h       | 0x00           |

| 12h       | 0x00           |

| 11h       | 0x00           |

| 0Bh       | 0x00           |

| 0Ah       | 0x1F           |

# Default Degister Val

# **Register Description**

# Address Description

| 18h | Serial Num                                                                                   | ber Byte 7                                                                                                  |                 |                       |                 |                 |               |            |  |

|-----|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-----------------|-----------------|---------------|------------|--|

|     | D7                                                                                           | D6                                                                                                          | D5              | D4                    | D3              | D2              | D1            | D0         |  |

|     | SN.63                                                                                        | SN.62                                                                                                       | SN.61           | SN.60                 | SN.59           | SN.58           | SN.57         | SN.56      |  |

|     | Upper byte o                                                                                 | f the serial nur                                                                                            | nber. Read/wri  | te when SNL=0         | 0, read-only wh | hen SNL=1. No   | onvolatile.   |            |  |

| 17h | Serial Num                                                                                   | ber Byte 6                                                                                                  |                 |                       |                 |                 |               |            |  |

|     | D7                                                                                           | D6                                                                                                          | D5              | D4                    | D3              | D2              | D1            | D0         |  |

|     | SN.55                                                                                        | SN.54                                                                                                       | SN.53           | SN.52                 | SN.51           | SN.50           | SN.49         | SN.48      |  |

|     | Byte 6 of the                                                                                | serial number.                                                                                              | Read/write wl   | hen SNL=0, rea        | ad-only when S  | SNL=1. Nonvo    | latile.       |            |  |

| 16h | Serial Num                                                                                   | ber Byte 5                                                                                                  |                 |                       |                 |                 |               |            |  |

|     | D7                                                                                           | D6                                                                                                          | D5              | D4                    | D3              | D2              | D1            | D0         |  |

|     | SN.47                                                                                        | SN.46                                                                                                       | SN.45           | SN.44                 | SN.43           | SN.42           | SN.41         | SN.40      |  |

|     | Byte 5 of the                                                                                | serial number.                                                                                              | Read/write wl   | hen SNL=0, rea        | ad-only when S  | SNL=1. Nonvo    | latile.       |            |  |

| 15h | Serial Num                                                                                   | ber Byte 4                                                                                                  |                 |                       |                 |                 |               |            |  |

|     | D7                                                                                           | D6                                                                                                          | D5              | D4                    | D3              | D2              | D1            | D0         |  |

|     | SN.39                                                                                        | SN.38                                                                                                       | SN.37           | SN.36                 | SN.35           | SN.34           | SN.33         | SN.32      |  |

|     | Byte 4 of the                                                                                |                                                                                                             |                 | hen SNL=0, rea        |                 |                 |               |            |  |

| 14h | Serial Num                                                                                   | ber Byte 3                                                                                                  |                 |                       |                 |                 |               |            |  |

|     | D7                                                                                           | D6                                                                                                          | D5              | D4                    | D3              | D2              | D1            | D0         |  |

|     | SN.31                                                                                        | SN.30                                                                                                       | SN.29           | SN.28                 | SN.27           | SN.26           | SN.25         | SN.24      |  |

|     | Byte 3 of the                                                                                | serial number.                                                                                              | . Read/write wl |                       | ad-only when S  |                 |               |            |  |

| 13h | Serial Num                                                                                   | Byte 3 of the serial number. Read/write when SNL=0, read-only when SNL=1. Nonvolatile. Serial Number Byte 2 |                 |                       |                 |                 |               |            |  |

|     | D7                                                                                           | D6                                                                                                          | D5              | D4                    | D3              | D2              | D1            | D0         |  |

|     | SN.23                                                                                        | SN.22                                                                                                       | SN.21           | SN.20                 | SN.19           | SN.18           | SN.17         | SN.16      |  |

|     |                                                                                              |                                                                                                             |                 | hen SNL=0, rea        |                 |                 |               |            |  |

| 12h | Serial Number Byte 1                                                                         |                                                                                                             |                 |                       |                 |                 |               |            |  |

|     | D7                                                                                           | D6                                                                                                          | D5              | D4                    | D3              | D2              | D1            | D0         |  |

|     | SN.15                                                                                        | SN.14                                                                                                       | SN.13           | SN.12                 | SN.11           | SN.10           | SN.9          | SN.8       |  |

|     |                                                                                              |                                                                                                             |                 | hen SNL=0, rea        |                 |                 |               |            |  |

| 11h | Serial Num                                                                                   | nber Byte 0                                                                                                 |                 |                       |                 |                 |               |            |  |

|     | D7                                                                                           | D6                                                                                                          | D5              | D4                    | D3              | D2              | D1            | D0         |  |

|     | SN.7                                                                                         | SN.6                                                                                                        | SN.5            | SN.4                  | SN.3            | SN.2            | SN.1          | SN.0       |  |

|     |                                                                                              |                                                                                                             |                 | n SNL=0, read         |                 |                 |               |            |  |

| 10h | Counter 2                                                                                    | MSB                                                                                                         |                 |                       |                 |                 |               |            |  |

|     | D7                                                                                           | D6                                                                                                          | D5              | D4                    | D3              | D2              | D1            | D0         |  |

|     | C2.15                                                                                        | C2.14                                                                                                       | C2.13           | C2.12                 | C2.11           | C2.10           | C2.9          | C2.8       |  |

|     | Event Counter 2 MSB. Increments on overflows from Counter 2 LSB. Battery-backed, read/write. |                                                                                                             |                 |                       |                 |                 |               |            |  |

| 0Fh | Counter 2                                                                                    | LSB                                                                                                         |                 |                       |                 |                 |               |            |  |

|     | D7                                                                                           | D6                                                                                                          | D5              | D4                    | D3              | D2              | D1            | D0         |  |

|     | C2.7                                                                                         | C2.6                                                                                                        | C2.5            | C2.4                  | C2.3            | C2.2            | C2.1          | C2.0       |  |

|     |                                                                                              |                                                                                                             |                 | rammed edge e         | event on CNT2   | input or overf  | lows from Cou | nter 1 MSB |  |

|     |                                                                                              | Battery-backe                                                                                               | d, read/write . |                       |                 |                 |               |            |  |

| 0Eh | Counter 1                                                                                    | 1                                                                                                           |                 |                       |                 |                 |               |            |  |

|     | D7                                                                                           | D6                                                                                                          | D5              | D4                    | D3              | D2              | D1            | D0         |  |

|     | C1.15                                                                                        | C1.14                                                                                                       | C1.13           | C1.12                 | C1.11           | C1.10           | C1.9          | C1.8       |  |

|     |                                                                                              |                                                                                                             | ements on over  | rflows from Co        | unter 1 LSB. E  | Battery-backed, | read/write.   |            |  |

| 0Dh | Counter 1                                                                                    | r                                                                                                           | 1               | I                     |                 | 1               |               | 1          |  |

|     |                                                                                              | D6                                                                                                          | D5              | D4                    | D3              | D2              | D1            | D0         |  |

|     | D7                                                                                           | Do                                                                                                          | 03              | 21                    |                 |                 |               |            |  |

|     | D7<br>C1.7<br>Event Counter                                                                  | C1.6                                                                                                        | C1.5            | C1.4<br>rammed edge e | C1.3            | C1.2            | C1.1          | C1.0       |  |

| 0Ch    | Event Co                                  | unter Contr        | ol                                  |                  |                        |                   |                                        |                      |

|--------|-------------------------------------------|--------------------|-------------------------------------|------------------|------------------------|-------------------|----------------------------------------|----------------------|

|        | D7                                        | D6                 | D5                                  | D4               | D3                     | D2                | D1                                     | D0                   |

|        | -                                         | -                  | -                                   | -                | RC                     | CC                | C2P                                    | C1P                  |

| RC     |                                           |                    | is bit to 1 takes ount events. Th   |                  |                        |                   | ng the system to                       | read the             |

| CC     | Counter Ca                                | scade. When        | CC=0, the ever                      | nt counters ope  | rate independe         | ently according   | to the edge prog                       |                      |

|        |                                           |                    |                                     |                  |                        |                   | bit counter. The                       |                      |

|        |                                           |                    | nost significant<br>. Battery-backe |                  | counter and C          | NTT is the cont   | rolling input. Bi                      | t C2P 1s             |

| C2P    |                                           |                    |                                     |                  | s when $C2P =$         | 1 C2P is "don"    | 't care" when CC                       | C=1 The value        |

|        | of Event C                                | ounter 2 may       | inadvertently in                    | crement if C21   | P is changed. I        | Battery-backed,   | read/write.                            |                      |

| C1P    |                                           |                    |                                     |                  |                        |                   | Event Counter                          | 1 may                |

| 0.01   |                                           | ě.                 | f C1P is change                     | ed. Battery-bac  | ked, read/writ         | e.                |                                        |                      |

| 0Bh    | Compani<br>D7                             | on Control<br>D6   | D5                                  | D4               | D3                     | D2                | D1                                     | D0                   |

|        |                                           | D0                 |                                     |                  |                        |                   |                                        |                      |

| SNL    | SNL<br>Sorial Num                         | -<br>har Laalt Cat | FC                                  | WP1              | WP0                    | VBC               | y read-only. SN                        | VTP                  |

| SINL   |                                           |                    | onvolatile, read                    |                  |                        | NL permanenti     | y read-only. SIN                       | L cannot be          |

| FC     | Fast Charg                                | e: Setting FC      | to '1' (and VB                      | C=1) causes a    | ~1 mA trickle          | charge current    | to be supplied o                       | n V <sub>BAK</sub> . |

|        |                                           |                    | bles the charge                     |                  |                        |                   |                                        |                      |

| WP1-0  | Write Prote                               | ect. These bits    | control the wri                     | te protection o  | f the memory           | array. Nonvolat   | tile, read/write.                      |                      |

|        | , T                                       | Write protect      | addresses                           | WP1 WP0          | )                      |                   |                                        |                      |

|        |                                           | None               | addresses                           | $\frac{11}{0}$ 0 | <u>,</u>               |                   |                                        |                      |

|        |                                           | Bottom 1/4         |                                     | 0 1              |                        |                   |                                        |                      |

|        |                                           | Bottom 1/2         |                                     | 1 0              |                        |                   |                                        |                      |

|        |                                           | Full array         |                                     | 1 1              |                        |                   |                                        |                      |

| VBC    |                                           |                    |                                     |                  |                        |                   | FC=1) trickle ch                       | arge current to      |

| VTP    |                                           |                    |                                     |                  |                        | t. Nonvolatile, 1 | read/write.<br>nvolatile, read/w       |                      |

| V 11   | VII SCICCI                                | . This on com      | iois uie ieset u                    | ip point for the | low VDD les            | et function. No   | iivolatile, reau/ w                    | THE.                 |

|        | 1                                         | Trip Voltage       | VTP                                 |                  |                        |                   |                                        |                      |

|        |                                           | 3.9V               | 0                                   |                  |                        |                   |                                        |                      |

|        |                                           | 4.4V               | 1                                   |                  |                        |                   |                                        |                      |

| 0Ah    |                                           | g Control          |                                     | •                | 1                      |                   | -                                      | 1                    |

|        | D7                                        | D6                 | D5                                  | D4               | D3                     | D2                | D1                                     | D0                   |

|        | WDE                                       | -                  | -                                   | WDT4             | WDT3                   | WDT2              | WDT1                                   | WDT0                 |

| WDE    |                                           |                    |                                     |                  |                        |                   | l to go active. W                      |                      |

|        | the timer ru                              | ins but has no     | effect on /RS1                      | , however the    | WTR flag will          | be set when a f   | fault occurs. Not<br>This assures a fi | e as the timer       |

|        |                                           |                    | Nonvolatile, rea                    |                  | C5-0 prior to 5        | ctting WDL 1.     | This assures a f                       | un watendog          |

| WDT4-0 | Watchdog                                  | Timeout. Indi      | cates the minim                     | num watchdog     |                        |                   | resolution. New                        |                      |

|        | timeouts ar                               | e loaded wher      | n the timer is re                   | started by writ  | ing the 1010b          | pattern to WR3    | -0. Nonvolatile,                       | read/write.          |

|        | Watchdog timeout WDT4 WDT3 WDT2 WDT1 WDT0 |                    |                                     |                  |                        |                   |                                        |                      |

|        |                                           | nvalid – defa      |                                     | 0                | $\frac{\sqrt{D13}}{0}$ | 0                 | 0                                      |                      |

|        |                                           | .00 ms             |                                     | 0                | 0 0                    | 0                 | 1                                      |                      |

|        | 2                                         | 200 ms             |                                     | 0                | 0 0                    | 1                 | 0                                      |                      |

|        | 3                                         | 300 ms             |                                     | 0                | 0 0                    | 1                 | 1                                      |                      |

|        |                                           | •<br>•             |                                     |                  |                        |                   |                                        |                      |

|        | 2                                         | 2000 ms            |                                     | 1                | 0 1                    | 0                 | 0                                      |                      |

|        |                                           | 2100 ms            |                                     | 1                | 0 1                    | 0                 | 1                                      |                      |

|        |                                           | 200 ms             |                                     | 1                | 0 1                    | 1                 | 0                                      |                      |

|        |                                           | •                  |                                     |                  |                        |                   |                                        |                      |

|        | ,<br>,                                    | 900 ms             |                                     | 1                | 1 1                    | 0                 | 1                                      |                      |

|        |                                           | 3000 ms            |                                     | 1                | 1 1                    | 1                 | 0                                      |                      |

|        |                                           | Disable count      | ter                                 | 1                | 1 1                    | 1                 | 1                                      |                      |

|        | _                                         |                    |                                     |                  | -                      |                   |                                        |                      |

| 09h   | Watchdog Restart & Flags                                                                                                                                                                                                                                                                                                                                                                                                                        |     |    |    |     |     |     |     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|----|-----|-----|-----|-----|

|       | D7                                                                                                                                                                                                                                                                                                                                                                                                                                              | D6  | D5 | D4 | D3  | D2  | D1  | D0  |

|       | WTR                                                                                                                                                                                                                                                                                                                                                                                                                                             | POR | LB | -  | WR3 | WR2 | WR1 | WR0 |

| WTR   | Watchdog Timer Reset Flag: When a watchdog timer fault occurs, the WTR bit will be set to 1. It must be cleared by the user. Note that both WTR and POR could be set if both reset sources have occurred since the flags were                                                                                                                                                                                                                   |     |    |    |     |     |     |     |

| POR   | cleared by the user. Battery-backed. Read/Write (internally set, user can clear bit).   Power-on Reset Flag: When the /RST pin is activated by either $V_{DD} < V_{TP}$ or a manual reset, the POR bit will be set to 1. It must be cleared by the user. Note that both WTR and POR could be set if both reset sources have occurred since the flags were cleared by the user. Battery-backed. Read/Write (internally set, user can clear bit). |     |    |    |     |     |     |     |

| LB    | Low Backup Flag: On power up, if the VBAK source is below the minimum voltage to operate the event counters, this bit will be set to 1. The user should clear it to 0 when initializing the system. Battery-backed. Read/Write (internally set, user can clear bit).                                                                                                                                                                            |     |    |    |     |     |     |     |

| WR3-0 | Watchdog Restart: Writing a pattern 1010b to WR3-0 restarts the watchdog timer. The upper nibble contents do not affect this operation. Writing any pattern other than 1010b to WR3-0 has no effect on the timer. This allows users to clear the WTR, POR, and LB flags without affecting the watchdog timer. Battery-backed, Write-only.                                                                                                       |     |    |    |     |     |     |     |

| 00-08h | <b>Reserved – DO NOT USE THIS ADDRESS SPACE</b> |

|--------|-------------------------------------------------|

# **Two-wire Interface**

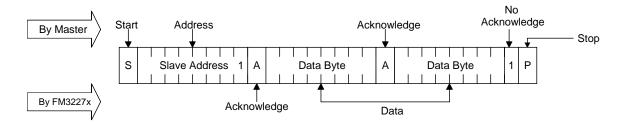

The FM3227x employs an industry standard twowire bus that is familiar to many users. This product is unique since it incorporates two logical devices in one chip. Each logical device can be accessed individually. Although monolithic, it appears to the system software to be two separate products. One is a memory device. It has a Slave Address (Slave ID = 1010b) that operates the same as a stand-alone memory device. The second device is a real-time clock and processor companion which have a unique Slave Address (Slave ID = 1101b).

By convention, any device that is sending data onto the bus is the transmitter while the target device for this data is the receiver. The device that is controlling the bus is the master. The master is responsible for generating the clock signal for all operations. Any device on the bus that is being controlled is a slave. The FM3227x is always a slave device.

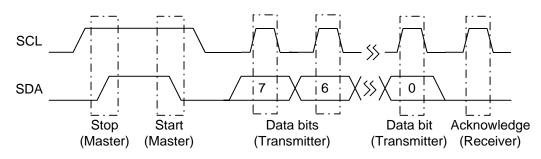

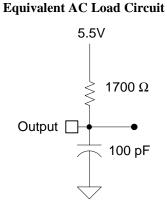

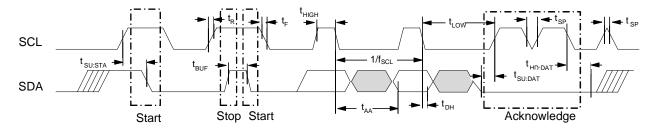

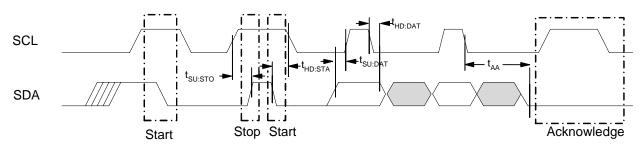

The bus protocol is controlled by transition states in the SDA and SCL signals. There are four conditions: Start, Stop, Data bit, and Acknowledge. The figure below illustrates the signal conditions that specify the four states. Detailed timing diagrams are shown in the Electrical Specifications section.

Figure 9. Data Transfer Protocol

#### Start Condition

A Start condition is indicated when the bus master drives SDA from high to low while the SCL signal is high. All read and write transactions begin with a Start condition. An operation in progress can be aborted by asserting a Start condition at any time. Aborting an operation using the Start condition will ready the FM3227x for a new operation.

If the power supply drops below the specified VTP during operation, any 2-wire transaction in progress will be aborted and the system must issue a Start condition prior to performing another operation.

#### **Stop Condition**

A Stop condition is indicated when the bus master drives SDA from low to high while the SCL signal is high. All operations must end with a Stop condition. If an operation is pending when a stop is asserted, the operation will be aborted. The master must have control of SDA (not a memory read) in order to assert a Stop condition.

#### Data/Address Transfer

All data transfers (including addresses) take place while the SCL signal is high. Except under the two

conditions described above, the SDA signal should not change while SCL is high.

#### Acknowledge

The Acknowledge (ACK) takes place after the 8<sup>th</sup> data bit has been transferred in any transaction. During this state the transmitter must release the SDA bus to allow the receiver to drive it. The receiver drives the SDA signal low to acknowledge receipt of the byte. If the receiver does not drive SDA low, the condition is a No-Acknowledge (NACK) and the operation is aborted.

The receiver might NACK for two distinct reasons. First is that a byte transfer fails. In this case, the NACK ends the current operation so that the part can be addressed again. This allows the last byte to be recovered in the event of a communication error.

Second and most common, the receiver does not send an ACK to deliberately terminate an operation. For example, during a read operation, the FM3227x will continue to place data onto the bus as long as the receiver sends ACKs (and clocks). When a read operation is complete and no more data is needed, the receiver must NACK the last byte. If the receiver ACKs the last byte, this will cause the FM3227x to attempt to drive the bus on the next clock while the master is sending a new command such as a Stop.

#### Slave Address

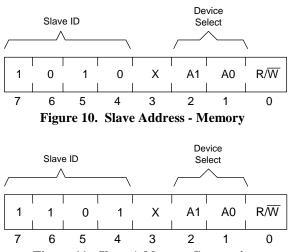

The first byte that the FM3227x expects after a Start condition is the slave address. As shown in figures below, the slave address contains the Slave ID, Device Select address, and a bit that specifies if the transaction is a read or a write.

The FM3227x has two Slave Addresses (Slave IDs) associated with two logical devices. To access the memory device, bits 7-4 should be set to 1010b. The other logical device within the FM3227x is the real-time clock and companion. To access this device, bits 7-4 of the slave address should be set to 1101b. A bus transaction with this slave address will not affect the memory in any way. The figures below illustrate the two Slave Addresses.

The Device Select bits allow multiple devices of the same type to reside on the 2-wire bus. The device select bits (bits 2-1) select one of four parts on a two-wire bus. They must match the corresponding value on the external address pins in order to select the device. Bit 0 is the read/write bit. A "1" indicates a read operation, and a "0" indicates a write operation.

Figure 11. Slave Address – Companion

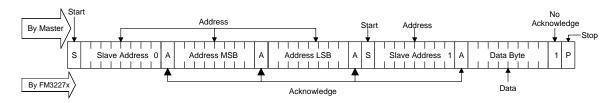

#### Addressing Overview – Memory

After the FM3227x acknowledges the Slave Address, the master can place the memory address on the bus for a write operation. The address requires two bytes. This is true for all members of the family. Therefore the 4Kb and 16Kb configurations will be addressed differently from stand alone serial memories but the entire family will be upwardly compatible with no software changes. The first is the MSB (upper byte). For a given density unused address bits are don't cares, but should be set to 0 to maintain upward compatibility. Following the MSB is the LSB (lower byte) which contains the remaining eight address bits. The address is latched internally. Each access causes the latched address to be incremented automatically. The current address is the value that is held in the latch, either a newly written value or the address following the last access. The current address will be held as long as VDD > VTP or until a new value is written. Accesses to the clock do not affect the current memory address. Reads always use the current address. A random read address can be loaded by beginning a write operation as explained below.

After transmission of each data byte, just prior to the Acknowledge, the FM3227x increments the internal address. This allows the next sequential byte to be accessed with no additional addressing externally. After the last address is reached, the address latch will roll over to 0000h. There is no limit to the number of bytes that can be accessed with a single read or write operation.

#### Addressing Overview – Companion

The Processor Companion operates in a similar manner to the memory, except that it uses only one byte of address. Addresses 00h to 18h correspond to special function registers. Attempting to load addresses above 18h is an illegal condition; the FM3227x will return a NACK and abort the 2-wire transaction.

# Data Transfer

After the address information has been transmitted, data transfer between the bus master and the FM3227x begins. For a read, the FM3227x will place 8 data bits on the bus then wait for an ACK from the master. If the ACK occurs, the FM3127x will transfer the next byte. If the ACK is not sent, the FM3227x will end the read operation. For a write operation, the FM3227x will accept 8 data bits from the master then send an Acknowledge. All data transfer occurs MSB (most significant bit) first.

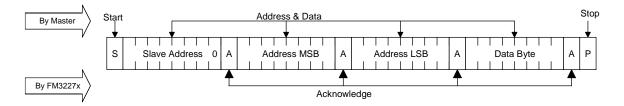

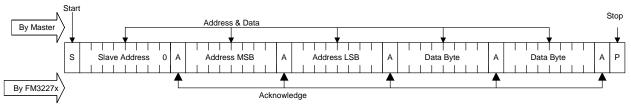

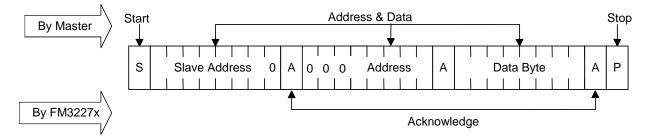

#### **Memory Write Operation**

All memory writes begin with a Slave Address, then a memory address. The bus master indicates a write operation by setting the slave address LSB to a 0. After addressing, the bus master sends each byte of data to the memory and the memory generates an Acknowledge condition. Any number of sequential bytes may be written. If the end of the address range is reached internally, the address counter will wrap to 0000h. Internally, the actual memory write occurs after the 8<sup>th</sup> data bit is transferred. It will be complete before the Acknowledge is sent. Therefore, if the user desires to abort a write without altering the

memory contents, this should be done using a Start or Stop condition prior to the 8<sup>th</sup> data bit. The figures below illustrate a single- and multiple-writes to memory.

Figure 12. Single Byte Memory Write

Figure 13. Multiple Byte Memory Write

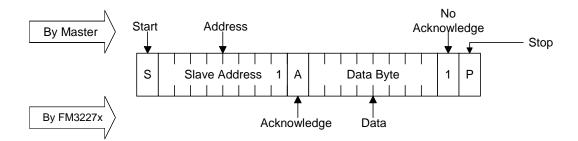

#### **Memory Read Operation**

There are two types of memory read operations. They are current address read and selective address read. In a current address read, the FM3227x uses the internal address latch to supply the address. In a selective read, the user performs a procedure to first set the address to a specific value.

#### Current Address & Sequential Read

As mentioned above the FM3227x uses an internal latch to supply the address for a read operation. A current address read uses the existing value in the address latch as a starting place for the read operation. The system reads from the address immediately following that of the last operation.

To perform a current address read, the bus master supplies a slave address with the LSB set to 1. This indicates that a read operation is requested. After receiving the complete device address, the FM3227x will begin shifting data out from the current address on the next clock. The current address is the value held in the internal address latch.

Beginning with the current address, the bus master can read any number of bytes. Thus, a sequential read is simply a current address read with multiple byte transfers. After each byte the internal address counter will be incremented. Each time the bus master acknowledges a byte, this indicates that the FM3227x should read out the next sequential byte.

There are four ways to terminate a read operation. Failing to properly terminate the read will most likely create a bus contention as the FM3227x attempts to read out additional data onto the bus. The four valid methods follow.

- 1. The bus master issues a NACK in the 9<sup>th</sup> clock cycle and a Stop in the 10<sup>th</sup> clock cycle. This is illustrated in the diagrams below and is preferred.

- 2. The bus master issues a NACK in the 9<sup>th</sup> clock cycle and a Start in the 10<sup>th</sup>.

- 3. The bus master issues a Stop in the 9<sup>th</sup> clock cycle.

- 4. The bus master issues a Start in the 9<sup>th</sup> clock cycle.

If the internal address reaches the top of memory, it will wrap around to 0000h on the next read cycle. The figures below show the proper operation for current address reads.

#### Selective (Random) Read

There is a simple technique that allows a user to select a random address location as the starting point

#### RAMTRON

for a read operation. This involves using the first three bytes of a write operation to set the internal address followed by subsequent read operations.

To perform a selective read, the bus master sends out the slave address with the LSB set to 0. This specifies a write operation. According to the write protocol, the bus master then sends the address bytes that are loaded into the internal address latch. After the FM3127x acknowledges the address, the bus master issues a Start condition. This simultaneously aborts the write operation and allows the read command to be issued with the slave address LSB set to a 1. The operation is now a read from the current address. Read operations are illustrated below.

#### **Companion Write Operation**

All Companion writes operate in a similar manner to memory writes. The distinction is that a different device ID is used and only one byte address is needed instead of two. Figure 16 illustrates a single byte write to this device.

#### **Companion Read Operation**

As with writes, a read operation begins with the Slave Address. To perform a register read, the bus master supplies a Slave Address with the LSB set to 1. This indicates that a read operation is requested. After receiving the complete Slave Address, the FM3227x will begin shifting data out from the current register address on the next clock. Auto-increment operates for the special function registers as with the memory address. A current address read for the registers look exactly like the memory except that the device ID is different.

The FM3227x contains two separate address registers, one for the memory address and the other for the register address. This allows the contents of one address register to be modified without affecting the current address of the other register. For example, this would allow an interrupted read to the memory while still providing fast access to a companion register. A subsequent memory read will then continue from the memory address where it previously left off, without requiring the load of a new memory address. However, a write sequence always requires an address to be supplied.

Figure 14. Current Address Memory Read

Figure 15. Sequential Memory Read

Figure 16. Selective (Random) Memory Read

#### Figure 17. Byte Register Write

Although not required, it is recommended that A5-A7 in the Register Address byte are zeros in order to preserve compatibility with future devices.

#### Addressing F-RAM Array in the FM3227x Family

The FM3227x family includes 256Kb, 64Kb, 16Kb, and 4Kb memory densities. The following 2-byte address field is shown for each density.

| Part #  | ľ |   | 1 <sup>st</sup> Address Byte |     |     |     |     |    | $2^{nd}$ | Addr | ess B | yte |    |    |    |    |    |

|---------|---|---|------------------------------|-----|-----|-----|-----|----|----------|------|-------|-----|----|----|----|----|----|

| FM32278 |   | х | A14                          | A13 | A12 | A11 | A10 | A9 | A8       | Α7   | Аб    | A5  | A4 | A3 | A2 | A1 | A0 |

| FM32276 |   | х | х                            | х   | A12 | A11 | A10 | A9 | A8       | Α7   | Аб    | A5  | A4 | A3 | A2 | A1 | A0 |

| FM32274 |   | х | х                            | х   | х   | х   | A10 | A9 | A8       | Α7   | Аб    | A5  | A4 | A3 | A2 | A1 | A0 |

| FM32272 |   | х | х                            | х   | х   | х   | х   | х  | A8       | Α7   | Аб    | A5  | A4 | A3 | A2 | A1 | A0 |

#### Table 4. Two-Byte Memory Address

# **Electrical Specifications**

#### **Absolute Maximum Ratings**

| Symbol            | Description                                          | Ratings                                           |

|-------------------|------------------------------------------------------|---------------------------------------------------|

| V <sub>DD</sub>   | Power Supply Voltage with respect to V <sub>SS</sub> | -1.0V to +7.0V                                    |

| V <sub>IN</sub>   | Voltage on any signal pin with respect to $V_{SS}$   | -1.0V to +7.0V * and $V_{IN} \le V_{DD}$ +1.0V ** |

| V <sub>BAK</sub>  | Backup Supply Voltage                                | -1.0V to +4.5V                                    |

| T <sub>STG</sub>  | Storage Temperature                                  | -55°C to + 125°C                                  |

| T <sub>LEAD</sub> | Lead Temperature (Soldering, 10 seconds)             | 300° C                                            |

| V <sub>ESD</sub>  | Electrostatic Discharge Voltage                      |                                                   |

|                   | - Human Body Model (JEDEC Std JESD22-A114-B)         | 3kV                                               |

|                   | - Charged Device Model (JEDEC Std JESD22-C101-A)     | 1kV                                               |

|                   | Package Moisture Sensitivity Level                   | MSL-1                                             |

\* PFI input voltage must not exceed 4.5V.

\*\* The " $V_{IN} < V_{DD}$ +1.0V" restriction does not apply to the SCL and SDA inputs which do not employ a diode to  $V_{DD}$ . Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only, and the functional operation of the device at these or any other conditions above those listed in the operational section of this specification is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

| Symbol             | Parameter                                                   | Min             | Тур | Max             | Units | Notes |

|--------------------|-------------------------------------------------------------|-----------------|-----|-----------------|-------|-------|

| V <sub>DD</sub>    | Main Power Supply                                           | 4.0             |     | 5.5             | V     | 7     |

| I <sub>DD</sub>    | $V_{DD}$ Supply Current<br>@ SCL = 100 kHz                  |                 |     | 500             | μA    | 1     |

|                    | $\overleftrightarrow{a}$ SCL = 400 kHz                      |                 |     | 900             | μA    |       |

|                    | $\overset{\frown}{@}$ SCL = 1 MHz                           |                 |     | 1500            | μΑ    |       |

| I <sub>SB</sub>    | Standby Current                                             |                 |     | 150             | μA    | 2     |

| V <sub>BAK</sub>   | Backup Supply Voltage                                       | 2.0             | 3.0 | 3.75            | V     | 9     |

| I <sub>BAK</sub>   | Backup Supply Current                                       |                 |     | 1               | μΑ    | 4     |

| I <sub>BAKTC</sub> | Trickle Charge Current with V <sub>BAK</sub> =0V            |                 |     |                 |       | 10    |

|                    | Fast Charge Off $(FC = 0)$                                  | 50              | -   | 120             | μΑ    |       |

|                    | Fast Charge On $(FC = 1)$                                   | 200             | -   | 2500            | μΑ    |       |

| V <sub>TP1</sub>   | $V_{DD}$ Trip Point Voltage, VTP = 0                        | 3.80            | 3.9 | 4.00            | V     | 5     |

| V <sub>TP2</sub>   | $V_{DD}$ Trip Point Voltage, VTP = 1                        | 4.25            | 4.4 | 4.50            | V     | 5     |

| V <sub>RST</sub>   | $V_{DD}$ for valid /RST @ $I_{OL}$ = 80 $\mu$ A at $V_{OL}$ |                 |     |                 |       | 6     |

|                    | $V_{BAK} > V_{BAK} \min$                                    | 0               |     |                 | V     |       |

|                    | $V_{BAK} < V_{BAK} \min$                                    | 1.6             |     |                 | V     |       |

| I <sub>LI</sub>    | Input Leakage Current                                       |                 |     | ±1              | μΑ    | 3     |

| I <sub>LO</sub>    | Output Leakage Current                                      |                 |     | ±1              | μΑ    | 3     |

| V <sub>IL</sub>    | Input Low Voltage                                           |                 |     |                 |       |       |

|                    | All inputs except those listed below                        | -0.3            |     | $0.3 V_{DD}$    | V     | 8     |